High reliability due to sequential fabrication of components without involving soldering joints.Ĥ. Low cost due to simultaneous production of a large number of chips in a batch.ģ. Merits of IC Technology Over Discrete Circuit TechnologyĢ. Ordinarily, a small parentage of these chips are faulty due to imperfections in manufacture. Thus, on taking say 20 wafers of size 1inch square in one production batch, we may fabricate 400×20 = 8000 ICs, each containing upto 50 elements i.e. Further IC chips are produced in batches. Hence, 1 important merit of IC technology. One element say, transistor or diode or resistor occupies area of about 5 mil 2, hence one IC chip of size 50 mils x 50 mils can accommodate 50 separate circuit elements. Order of Packing: Let one-inch square Si wafer be cut into say 400 square chips each of size 50 mils x 50 mils. One surface of the wafer is lapped and polished to remove surface imperfections.

This is cut into round wafers, approximately 6 mils thick. This ingot is typically 1 to 2 inches in diameter and about 10 inches in length. The p-type substrate is obtained from silicon ingot grown from s silicon melt of desired high purity. Finally, a fourth layer, described as L4 in figure 2 using metal typically aluminum is added at the top in selected regions to permit interconnections between the various elements. This SiO2 layer serves the additional function of protecting the silicon wafer against contamination. The selective etching of SiO2 layer is achieved by subjecting the SiO2 layer to a photolithographic process. The SiO2 layer is etched away from the region where diffusion is desired to be permitted, while the rest of the wafer remains protected against diffusion. Hence, a thin SiO2 layer 元 is formed at top and used as mask. This selective distribution is obtained by using silicon dioxide layer at the top as the barrier protecting portions of silicon wafer against impurities diffusion. Out of the various components so fabricated, the transistor requires the maximum number of fabricated simultaneously with the fabrication of transistor using one or more of the steps involved in the fabricated of a transistor.įabrication of various circuit elements requires selective diffusion of impurities, p-type or n-type, over certain precisely defined regions within n-type second layer L2.

XSECTION OF IC CHIP SERIES

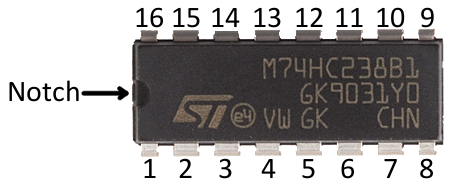

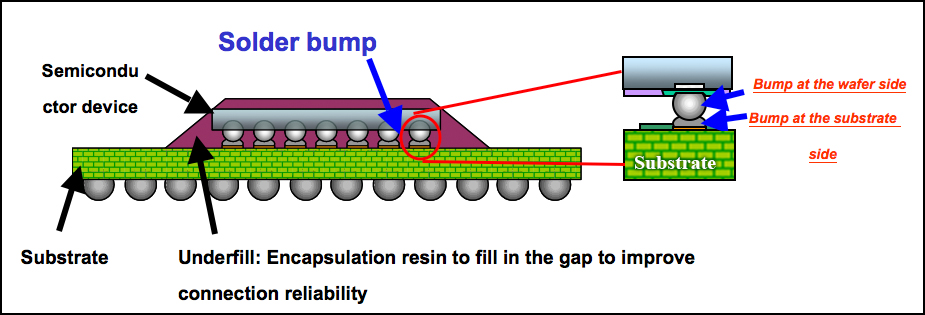

All active and passive elements such as transistors, diodes, resistors, and capacitors are built within this layer L2 using series of p-type and n-type impurities diffusions. The second layer L2 typically 1 mil (25 um) thick, is an n-type silicon which is grown as a single crystal extension of the substrate. The bottom most layer L1, typically 6 mil thick, is a p-type silicon and it forms the substrate or the foundation upon which the complete integrated circuit is formed. The structure shown in figure 2 consists of 4 layers of materials designated as L1, L2, 元 and L4. The fabrication technology of integrated circuit is basically planer diffusion technology. Figure 2 gives the cross-sectional view of the integrated circuit corresponding to the circuit of figure 1. Basic IC Technologyįigure 1 shows a simple circuit containing a diode, a resistor and a transistor. Hence, these IC chips have identical characteristics. But in IC technology, all the circuit elements as ell as interconnections are fabricated as ta time. The processes used in the fabrication of these IC chips are basically the same as used in the fabrication of discrete transistors, diodes etc. Passive elements such as diodes, resistors, capacitors etc. chip typically having cross-section of 1 mm by 1 mm contains 1. Finally, each accepted IC chip is soldered to a package substrate for wire-bonding.One single silicon I.C. Each IC chip under inspection is then classified into one of three categories: accept, or reject, or to be reworked. Such a transformed or coded image is then examined to detect existent IC defects. A task-dependent, context-dependent image filter is designed to transform the IC image into another image so that at any moment only relevant information is emphasized while irrelevant information is suppressed. The macroregistration is achieved by locating the mask frame first, and each mask subpattern is microregistered independently by means of the proposed unnormalized cross correlation of contrast method.

XSECTION OF IC CHIP REGISTRATION

The image registration is then carried out in two steps. An input chip image is first segmented so that the IC image can be extracted. An integrated system on the basis of such a formulation is then proposed for the automatic visual inspection and wire-bonding of integrated circuit (IC) chips. A formulation of an automatic visual inspection and final packaging system is presented in this paper.

0 kommentar(er)

0 kommentar(er)